隨著技術的進步,EMI 對電路正常運行構成越來越大的威脅。這是因為電子應用正轉向各種無線通信或者便攜式平臺。因此大多數干擾 EMI 信號最終都以傳導 EMI 的形式進入到 PCB 線跡(trace)中。

當您努力想要設計出一種抗 EMI 電路時,您會發現,模擬傳感器電路往往會成為巨大的 EMI 吸收器。這是因為,傳感器電路常常產生低電平信號,并且有許多高阻抗模擬端口。另外,這些電路使用更加緊湊的組件間隔,其讓系統更容易截獲和傳導噪聲干擾,從而進入到線跡中。

在這種 EMI 情況下,運算放大器 (op amp) 便會成為一個主要目標。我們在本系列文章的第1部分“EMI 如何通過介質干擾電路”看到了這種效應,此文中圖 1 所示 EMI 信號引起 1.5 伏的偏移電壓誤差!

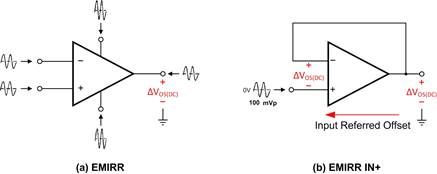

一個標準的運算放大器有 3 個低阻抗引腳(正功率、負功率和輸出)以及 2 個高阻抗輸入引腳(請參見圖 1a)。盡管這些引腳可以抵抗 EMI 影響,但是輸入引腳最為脆弱。

圖 1 EMIRR 與 EMIRR IN+ 測定方法比較

EMIRR 電磁干擾抑制比

電壓反饋放大器的反相和非反相引腳的特性基本相同。但是,非反相輸入(請參見圖 1b)的放大器 EMI 耐受度測試最為簡單。

方程式 1

方程式 1 中,VRF_PEAK 為所用 RF 電壓的峰值,VOS 為放大器的 DC 偏移電壓,而 100 mVP 為 100 mVP 輸入信號 EMIRR IN+ 參考。

您可以利用 EMIRR 衡量標準,比較放大器的 EMI 抑制性能。圖 2 顯示了 TI OPA333 CMOS 運算放大器的 EMIRR IN+ 響應。該圖表明,這種器件可以較好地抑制器件300 kHz帶寬以上的頻率信號。

- 1

- 2

- 總2頁

來源:互聯網

http:m.mangadaku.com/news/2012-11/20121116164210.html